# Development of Substrates Featuring Through Glass Vias (TGV) for 3D-IC Integration

Authors: Aric Shorey, Scott Pollard, Alex Streltsov, Garret Piech, Robert Wagner Corning Incorporated Corning, New York 14831

ShoreyAB@corning.com

#### Abstract

Through-substrate vias (TSV) are critical for Three-Dimensional Integrated Circuit (3D-IC) integration. While silicon traditionally has been used in this application, glass has properties that make it a very intriguing material for through substrate via applications. We note that the term glass describes a broad material set, with a wide range of properties driven by composition. For example, compositional changes allow tailoring of mechanical and thermal properties. Furthermore, novel forming processes available today enable reduction or elimination of time consuming and costly thinning or polishing processes, as well as opportunities to more easily scale the footprint of the substrate. Significant progress has been made to develop techniques to provide suitable through holes for vias in different glass compositions, which leverages the versatility of glass to create a substrate for TSV.

#### Introduction

There are two primary challenges to fabricating a precision interposer using thin glass. The first is obtaining high quality thin glass wafers (300 mm OD, thickness 0.05 to 0.10 mm, warp and total thickness variation (TTV) of 30  $\mu$ m and 1  $\mu$ m respectively). The second challenge is developing a cost-effective process capable of providing small (5-10  $\mu$ m) and high-precision through holes.

The first step in developing TGV is to identify the most appropriate glass composition for the application, which furthermore defines important properties such as coefficient of thermal expansion (CTE) and other mechanical properties, electrical properties and chemical durability (during downstream processes and reliability testing). The manufacturing process used to develop the glass has a significant impact on quality and manufacturability. Fusion formed glass provides a solution for high volume manufacturing supply in an as-formed, ultra-thin, pristine glass manufactured to tight tolerances, and circumvents the issues associated with polishing or thinning. The supply of as-formed ultra-thin glass wafers less than 100  $\mu$ m thick can compare very favorably in cost relative to polished or thinned glass as well as thinned silicon wafer.

While there are many technologies that have demonstrated through holes in glass, challenges relating to via size and pitch, wafer strength and reliability remain to be resolved. However, substantial progress has been made to meet these challenges. Specific characterization data from some of these processes, that demonstrate through holes on the order of 10  $\mu$ m diameter with a 100  $\mu$ m glass thickness will be presented.

## **Glass Substrates**

Corning has been providing glass solutions for a variety of industrial and consumer applications for more than 160 years. Among recent applications enabled by Corning's precision flat glass process technology is liquid crystal display (LCD) substrate and cover glass for innovative electronic devices from smart phones to slates and TVs. This platform is an attractive option for supplying high volume substrate material for the semiconductor industry.

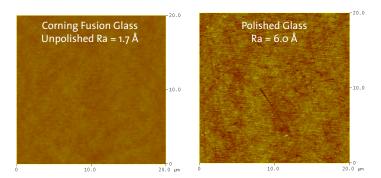

The history of Corning glass for LCD displays was recently published, highlighting the fusion process for making glass [1, 2]. In this process the glass flows over the edges on both sides of a trough rejoining underneath (see Figure. 1). The pristine outer surfaces of the glass do not touch any of the forming surfaces. As a result, the surface of the glass is extremely smooth as shown by the atomic force microscopy images in Figure 2.

Figure 1. The corning fusion process

Figure 2. Atomic force micrograph result

Maintaining exceptional flatness and minimal substrate TTV is important for 2.5D-IC and 3D-IC applications. A critical feature of the fusion process for LCDs is its ability to minimize thermal stress effects in the glass. With very little thermal stress in the glass, the warp can be very low. Enhancements to the fusion draw process can also be leveraged to produce wafers with exceptionally low TTV. Production of 300 mm diameter wafers with TTV < 2  $\mu$ m is readily available today. Because no polishing is required, this allows for easier volume scaling and positively impacts substrate reliability.

Additional advantages of using the fusion process for generating TGV substrates derive from process flexibility for size and thickness. Since the fusion process provides sheets with dimensions of more than three meters, it is straightforward to provide wafers of almost any size. Wafers up to 450 mm in size are readily manufactured today and providing substrates in a panel format is straight forward. Furthermore, high-quality substrates < 100 um thick, can be provided for TGV substrates at target thickness with no grind and polish required. The advantages provided by ultra-slim flexible glass are highlighted in Figure 3.

Figure 3: Manufacture of high quality ultra-slim flexible glass provides substantial opportunities to deliver substrates for TGV that do not require thinning.

|                            | Glass A | Glass B |

|----------------------------|---------|---------|

| Density (g/cm³)            | 2.38    | 2.42    |

| CTE (ppm/oC) (o-3000C)     | 3.2     | 8.0     |

| Young's Modulus (GPa)      | 74      | 72      |

| Vickers Hardness (200g)    | 640     | 534     |

| Dielectric Constant (1kHz) | 5.3     | 7.0     |

Table 1: Range of properties for two glass types

Silicon is an ultrapure material with explicit material properties. Glass, on the other hand, represents a broad material set with properties dependent on the specific glass composition [3]. In addition to important dimensional attributes that can be leveraged from the fusion process, Corning's deep history in Display and other applications allows for developing glass compositions with tailored properties, such as targeted CTE. Table 1 provides an illustration of different material properties for two different fusion formed glass compositions. This gives an opportunity to affect total deformation of a bonded stack in 2.5D-IC and 3D-IC applications. Optimization of composition to affect properties such as CTE can also affect other characteristics such as electrical properties. Understanding these effects, and how to manage them, can be a particularly important consideration in TGV applications.

## **Strength Parameters**

Wafer breakage is a major concern in semiconductor manufacturing lines since it results in significant costs and disruptions. Silicon wafers typically break by brittle fracture and often by cleaving along crystallographic planes. The primary failure mode for glass is by brittle fracture. For both materials their strength depends on the presence of flaws (micro-cracks, etch pits, etc.), rather than the intrinsic bond strength of their material composition. When more flaws exist of increasing size, there is a higher statistical probability that failure will occur at the point where loads/stresses are applied to the wafer during manufacturing processes. This increases the importance of methods used in wafer preparation, such as grinding and polishing processes [4]. In the next sections, we discuss some baseline data on the practical strength of glass and silicon.

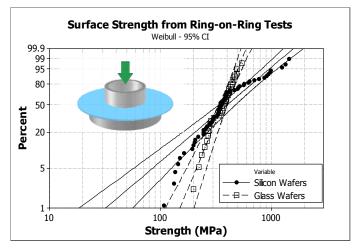

Even though the fracture modes can be different it is useful to compare the fracture strength of a silicon wafer surface to a glass wafer surface by using standardized test methods. A ring-on-ring test is appropriate for surfaces. The ring-on-ring technique consists of two concentric rings. The larger ring is positioned on the bottom, the smaller ring on top and the wafer under test placed between the two rings. The force is applied to the top ring creating a region of uniform tensile strain in the lower surface of a wafer material. The applied force is increased until failure occurs by fracture from a flaw.

Figure 4. Ring-on-ring results for glass and silicon wafers

A significant advantage of Corning's fusion process is that it provides an extremely high quality and precision surface that exhibits high strength, without the need for post forming processing. This avoids potentially introducing strength limiting flaws during the grinding/polishing. To evaluate the statistical nature of the failures it is useful to put the fracture data onto a Weibull plot. Figure 4 shows a Weibull distribution of 300 mm diameter silicon wafers (0.7 mm thick) and glass wafers (0.5 mm thick). The median strength values are almost identical for both materials. The relatively steep slope given by the glass wafers in Figure 4 indicates a more repeatable and predictable performance in glass, that avoiding the very low strength specimens seen in the silicon population. While all of the data in Fig. 4 is for unmodified wafers, we note that if holes are added to the wafers for vias, this can adversely affect the overall strength of the wafer. If the via manufacturing process introduces micro cracks in the sidewalls, the impact on wafer strength may be substantial. It is important to understand effects such as these as they will affect the overall reliability of the product. Additional work is underway so that we can better understand how through hole generation may impact overall strength and reliability of TGV substrates.

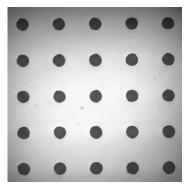

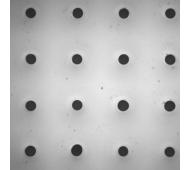

(A) Through Hole- top diameter ~30 µm, 100 µm pitch

(B) Through Hole- bottom diameter ~20 µm, 100 um pitch

(C) Blind Hole - top diameter 45 µm 100 µm pitch

(D) 20 µm top diameter, 50 µm pitch

Figure. 5: Various through vias and blind vias that have been demonstrated in thin glass substrates.

## Vias

There are numerous methods to form holes in glass for TGV. These include mechanical (drill, powder blast), chemical (wet, Corning Incorporated dry, photo-sensitive glass) and laser based methods. There are www.corning.com/semiglass pros and cons to each method used with challenges presented by the ability to scale in size, achieve acceptable sidewall One Houghton Park roughness (and associated mechanical reliability), overall cost Corning, New York and throughput. Variations in targeted properties, such as blind USA vs. through vias, sidewall shape/roughness and aspect ratio also provide challenges. Figure 5 shows some examples of various through via sizes, shapes, and qualities, that can be achieved. Email: semiglass@corning.com

High quality glass given by the fusion process gives a significant advantage in the cost effectiveness of the process. Generating high precision and high quality vias in substrates at the targeted thickness, thus avoiding time consuming and costly manufacturing steps and additional handling, provides substantial advantages for TGV.

## Conclusions

Successful implementation of through substrate vias is extremely important for 2.5D-IC and 3D-IC. Glass has numerous attributes that make TGV attractive for many applications. The ability to tailor properties (e.g. thermal and electrical) for specific applications provides tremendous advantage. The optimized fusion process provides important attributes such as excellent surface quality, low warp and TTV, and also provides valuable flexibility with respect to substrate size and thickness. The ability to make large wafers at target thickness and thus avoiding finishing, gives additional advantages with respect to manufacturing cost and economies of scale. While much progress has been demonstrated, the key challenge going forward is developing economically feasible methods to provide holes in the glass with targeted size, shape, quality (e.g. roughness) and reliability.

## Acknowledgements

The authors would like to acknowledge important contributions from Daniel Harvey and James Watkins.

#### References

300 µm

[1] Adam Ellison and Iván A. Cornejo, Glass Substrates for Liquid Crystal Displays, International Journal of Applied Glass 1 [1] 87-103 (2010)

[2] S. M. Dockerty and G. C. Shay, "Down flow Sheet Drawing Method and Apparatus," U.S. Patent No. 3149949, published September 22, 1964.

[3] Bocko, Lee, Information Display; 24(5-6): 26-30 (2008)

[4] P.-Y. Chen, M.H. Tsai, W-K. Yeh, M-H Jing, Y. Chang, "Relationship between wafer edge design and its ultimate mechanical strength", Microelectronic Engineering 87: 2065-2070 (2010).

Phone: 1 607 974 6250